Общая информация

Программируемая логическая интегральная схема (ПЛИС)

Дата последнего обновления документации 14.07.2025

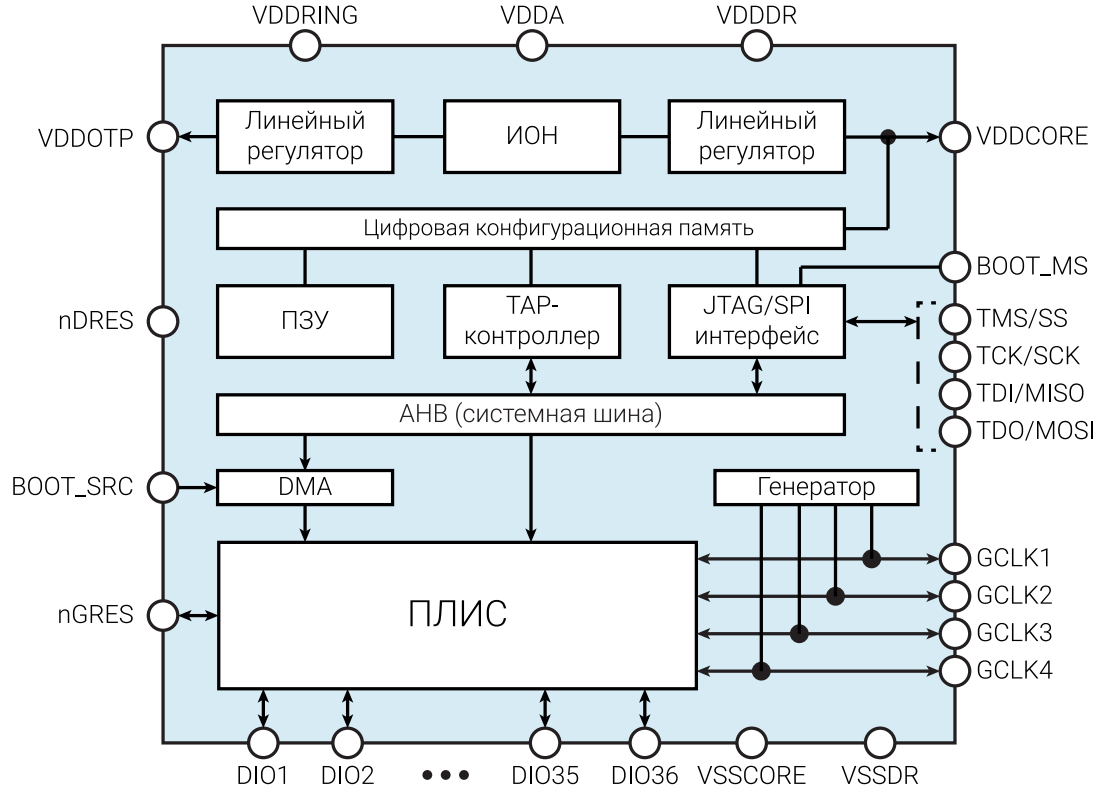

Микросхема 5400ТС015 – программируемая логическая интегральная схема (ПЛИС) для реализации на стороне пользователя различных логических схем или схем управления. Микросхема в своем составе содержит 1058 логических элементов. Каждый логический элемент состоит из трехвходового LUT и D-триггера.

ПЛИС имеет три способа конфигурирования памяти:

- конфигурирование из внутренней ПЗУ (режим энергонезависимой памяти);

- запись данных из внешней Flash-памяти;

- конфигурирование с помощью программатора напрямую в ОЗУ или ПЗУ.

При конфигурировании ПЛИС из внутренней ПЗУ, используется DMA-контроллер (Direct Memory Access), который обеспечивает загрузку данных в ОЗУ. ПЛИС содержит 36 программируемых пользовательских площадки ввода-вывода, а также 4 площадки ввода-вывода для глобальных тактовых сигналов.

Особенности

- 1058 логических элементов (трехвходовой LUT + D-триггер);

- Количество портов ввода/вывода 36;

- Частота внутреннего генератора 10 МГц;

- Задержка переключения логического элемента не более 5,0 нс;

- Диапазон напряжения питания: VDDA = 3,3 В … 5,0 В;

- Диапазон напряжения питания интерфейсной части: VDDDR = 2,5 В … 5,0 В;

- Возможность выбора устройства конфигурирования памяти: внутреннее ПЗУ, внешняя ПЗУ, программатор.

- Температурный диапазон от –60°С до +85°С

Электрические характеристики

| Параметр, единица измерения | Не менее | Типовое | Не более |

|---|---|---|---|

| Задержка переключения программируемого логического элемента, нс | 5,0 | ||

| Максимальная внешняя частота синхросигнала, МГц | |||

| • при VDDDR = 2,5 В | 8,0 | 8,0 | 20 |

| • при VDDDR = 5,0 В | 15 | 8,0 | 20 |

| Статический ток потребления, мА | 30 | ||

| Напряжение низкого уровня выходных цифровых сигналов, В | 0 | 0,4 | |

| Напряжение высокого уровня выходных цифровых сигналов, В | VDDDR–0,4 | VDDDR | |

| Частота внутреннего генератора, МГц | 9,7 | 10 | 10,3 |

Допускается подавать VDDDR=2,5 В…5,0 B при любом напряжении питания VDDA

Электростатическая защита

Микросхема имеет встроенную защиту от электростатического разряда до 500В (аналоговые выводы) и 2000В (цифровые выводы) по модели человеческого тела. Требует мер предосторожности.

Предельно-допустимые и предельные режимы эксплуатации

| Параметр, единица измерения | Предельно-допустимый режим | Предельный режим | ||

|---|---|---|---|---|

| не менее | не более | не менее | не более | |

| Напряжение питания аналоговой части (VDDA), В | 3,15 | 5,25 | −0,3 | 5,5 |

Напряжение питания ESD-защиты (VDDRING)(1), В | 3,15 | 5,25 | −0,3 | 5,5 |

| Напряжение питания интерфейсной части (VDDDR), В | 2,25 | 5,25 | –0,3 | 5,5 |

| Напряжение низкого уровня входных цифровых сигналов, В | –0,1 | 0,25хVDDDR | –0,3 | 5,5 |

| Напряжение высокого уровня входных цифровых сигналов, В | 0,75хVDDDR | VDDDR+0,25(2) | –0,3 | 5,5 |

| Ток нагрузки (DIO1–DIO36, GCLK1–GCLK4), мА | ||||

| • при VDDDR = 5,0 В | 10 | 20 | ||

| • при VDDDR = 3,3 В | 6,0 | 20 | ||

| • при VDDDR = 2,5 В | 1,0 | 20 | ||

| Максимальная рассеиваемая мощность, Вт | 2,0 | 3,0 | ||

| Температура эксплуатации, °С | -60 | +85 | –60 | +150 |

- рекомендуемое напряжение питания на вывод VDDRING – 5,0 В

- не более 5,25 В

Конфигурация и функциональное описание выводов

| № | Тип вывода | Наименование вывода | Назначение вывода |

|---|---|---|---|

| 1 | DI/DO | DIO18 | Цифровой вход/выход 18 |

| 2 | DI/DO | DIO17 | Цифровой вход/выход 17 |

| 3 | DI/DO | DIO16 | Цифровой вход/выход 16 |

| 4 | DI/DO | DIO15 | Цифровой вход/выход 15 |

| 5 | DI/DO | DIO14 | Цифровой вход/выход 14 |

| 6 | DI/DO | DIO13 | Цифровой вход/выход 13 |

| 7 | DI/DO | DIO12 | Цифровой вход/выход 12 |

| 8 | DI/DO | DIO11 | Цифровой вход/выход 11 |

| 9 | DI/DO | DIO10 | Цифровой вход/выход 10 |

| 10 | DI/DO | DIO9 | Цифровой вход/выход 9 |

| 11 | DI/DO | DIO8 | Цифровой вход/выход 8 |

| 12 | DI/DO | DIO7 | Цифровой вход/выход 7 |

| 13 | DI/DO | DIO6 | Цифровой вход/выход 6 |

| 14 | PWR | VSSDR | Общий вывод интерфейсной части |

| 15 | PWR | VDDDR | Вывод напряжения питания интерфейсной части |

| 16 | DI/DO | GCLK4 | Вывод глобального тактового сигнала 4 |

| 17 | DI/DO | GCLK3 | Вывод глобального тактового сигнала 3 |

| 18 | PWR | VDDCORE | Вывод для подключения шунтирующего конденсатора питания ядра |

| 19 | PWR | VSSCORE | Общий вывод питания ядра |

| 20 | DI/DO | DIO5 | Цифровой вход/выход 5 |

| 21 | DI/DO | DIO4 | Цифровой вход/выход 4 |

| 22 | DI/DO | DIO3 | Цифровой вход/выход 3 |

| 23 | DI/DO | DIO2 | Цифровой вход/выход 2 |

| 24 | DI/DO | DIO1 | Цифровой вход/выход 1 |

| 25 | DI | BOOT_SRC | Вывод выбора источника аппаратной загрузки данных в ОЗУ лог. «1» – внешнее ПЗУ лог. «0» – внутреннее ПЗУ |

| 26 | DI | BOOT_MS | Вывод выбора режима программирования лог. «1» – SPI (Master) лог. «0» – JTAG (Slave) |

| 27 | DI/DO | TMS/SS | Входной сигнал управления TAP-контроллером интерфейса JTAG / Выходной разрешающий сигнал SPI (SS) |

| 28 | DI | TDI/MISO | Входной сигнал JTAG / вход передачи данных SPI (MISO) |

Рекомендуемая схема применения

C1–C5 - 100 нФ

Описание функционирования микросхемы

Микросхема представляет собой программируемую логическую интегральную схему (ПЛИС) для реализации на стороне пользователя различных логических схем или схем управления.

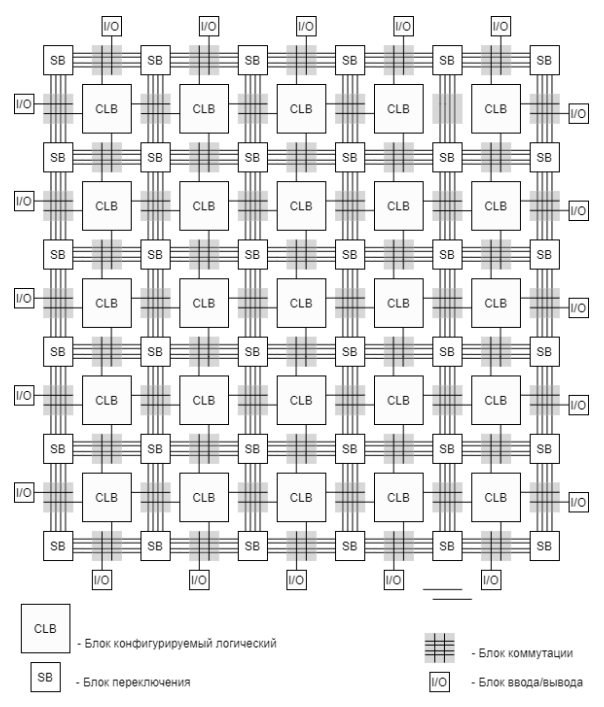

Блок ПЛИС

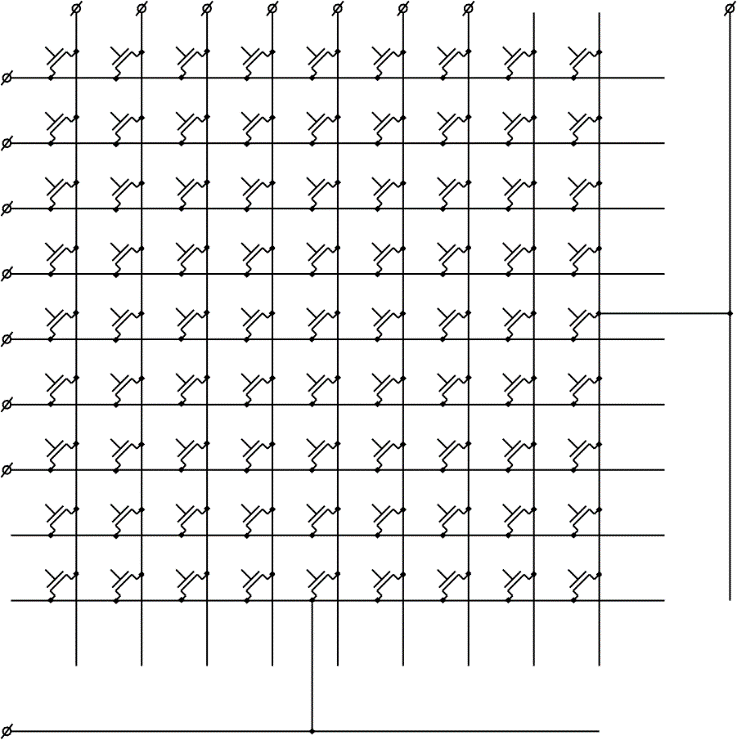

ПЛИС представляет из себя матричную структуру и состоит из следующих основных блоков:

- Блок конфигурируемый логический;

- Блок коммутации;

- Блок переключения;

- Матрица ячеек памяти.

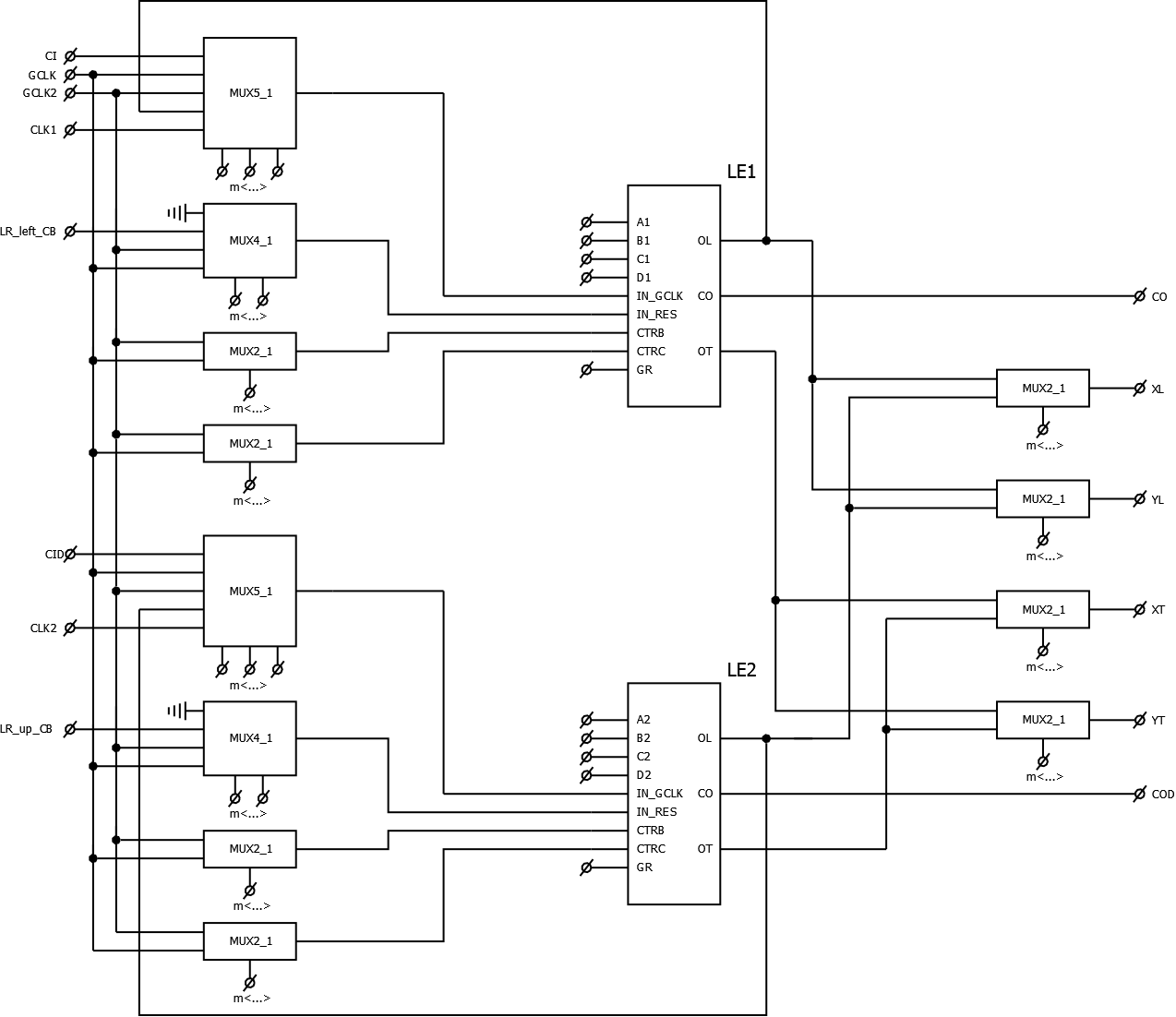

Блок конфигурируемый логический

Блок конфигурируемый логический (CLB) является основным функциональным элементом матрицы ПЛИС. В его состав входит 2 логических элемента (LE – Logic Element), а также элементы коммутации.

Каждый логический элемент блока ПЛИС состоит из трехвходового LUT и D-триггера.

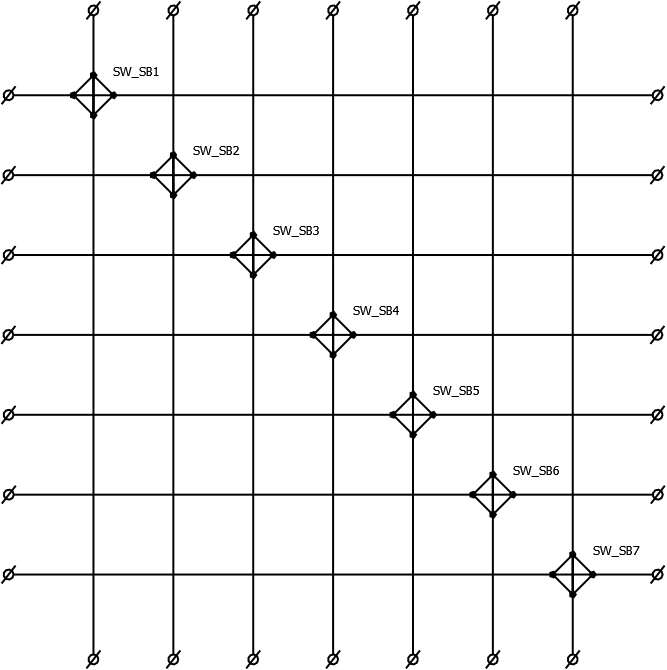

Блок переключений

Блок переключений (SB) состоит из 7-ми сложных ключей. Структурная схема блока S изображена на рисунке ниже.

Каждый ключ (SW_SB) блока SB имеет возможность коммутировать сигнал в любом направлении, а также мультиплексировать сигнал.

Блок коммутации

Блок коммутации (CB) состоит из матрицы аналоговых ключей 9x9. Ключи позволяют коммутировать сигналы между входами и выходами соседних логических блоков, а также соединять перенаправлять сигналы на блок SB и на две глобальные шины.

Ключ блока коммутации CB представляет собой простейший КМОП-ключ.

Напряжения питания микросхемы

Напряжение питания микросхемы от 3,3 В до 5,0 В. Напряжение питания ядра микросхемы (VDDCORE) и встроенного ПЗУ (VDDOTP) формируется с помощью внутреннего линейного регулятора. Напряжение питания DDD от 2,5 В до 5,0 В задает высокие логические уровни по пользовательским выводам, не влияя на логические уровни ядра. Допускается подавать VDDDR=2,5 В…5,0 B при любом напряжении питания VDDA.

RC-генератор

Встроенный RC-генератор с частотой 10 МГц позволяет тактировать внутренние цифровые интерфейсы, а также его можно использовать в качестве тактового сигнала для ПЛИС. Выход RC-генератора можно коммутировать на внешние выводы GCLK1-GCLK4.

Программирование

Формат программы для ПЛИС

Образ программы, прошиваемый в ПЛИС, имеет два формата представления: сжатый и несжатый. Несжатый формат содержит 676 x 678 + 8 + 9 бит данных, записываемых в ПЛИС непрерывным потоком напрямую в ОЗУ, и позволяет работать только в энергозависимом режиме.

8 дополнительных бит содержат настройку системы тактирования; 9 дополнительных бит содержат настройку статически конфигурируемых выводов и программируются в энергонезависимый режим через выводы CFGCLK и CFGDIN.

Размер несжатого образа не позволяет записать его во внутреннее ПЗУ микросхемы. Сжатый образ формируется из несжатого и позволяет сконфигурировать внутреннее ПЗУ для работы в энергонезависимом режиме. Программирование ПЗУ может производиться только сжатым образом.

Режимы программирования ПЛИС

Программирование через интерфейс JTAG:

- Запись во внутреннее ПЗУ сжатого образа;

- Запись в ОЗУ несжатого образа.

Программирование через интерфейс SPI. В данном режиме микросхема переходит к загрузке пользовательской конфигурации после подачи питания и выхода из сброса:

- Чтение из внешней SPI-совместимой Flash-памяти (1636РР4У) несжатого образа;

- Чтение из внешней SPI-совместимой Flash-памяти (1636РР4У) сжатого образа.

SPI интерфейс

При программировании по интерфейсу SPI микросхема считается «ведущим» устройством, которая по линии MOSI посылает код инструкции «ведомому» устройству, а также адресные биты. Ответ на команды управления должны приходить по линии MISO в текущем пакете данных объемом в 1 байт.

Режим работы SPI интерфейса master, MSB first, CPOL=0, CPHA= 0. Для выбора режима программирования ПЛИС по интерфейсу SPI необходимо установить на выводах BOOT_SRC и BOOT_MS высокий логический уровень.

Интерфейсные сигналы управления и частоту обеспечивает микросхема ПЛИС.

ПЛИС ориентирована на работу с микросхемой Flash-памяти 1636РР4У.

Команды SPI-интерфейса

| Команда | Код команды |

|---|---|

| Чтение массива данных из внешнего устройства | 03h 0000 0011 |

Проектирование

Создание проектов

Проектирование «зашивки» для ПЛИС осуществляется Verilog-описанием с последующим синтезом с помощью программного обеспечения Yosys. Программирование «зашивок» в ОЗУ и ПЗУ производится программатором через интерфейс JTAG.

Цифровые пользовательские площадки ввода/вывода DIO и GCLK

Цифровые площадки ввода/вывода DIO и GCLK типа GPIO позволяют пользователю конфигурировать направление сигнала, а также задавать высокий логический уровень с помощью внешне подключаемого питания DDD . Программирование пользовательских площадок происходит с помощью выводов CFGDIN и СFGCLK. В структуре ПЛИС имеются 36 пользовательских площадок ввод/вывода и 4 пользовательские площадки ввода/вывода тактовой частоты.

Конфигурация направлений пользовательских площадок ввода/вывода может быть как статической, так и динамической. Динамические выводы могут менять направление сигнала в процессе отладки или работы пользовательской конфигурации ПЛИС. Статические – конфигурируются из внутренних регистров и не имеют возможности менять направление. Однако динамические площадки также могут работать статично при соответствующей пользовательской конфигурации.

Динамические пользовательские площадки ввода/вывода: DIO2, DIO3, DIO4, DIO6, DIO7, DIO8, DIO10, DIO11, DIO12, DIO14, DIO15, DIO16, DIO18, DIO19, DIO20, DIO22, DIO23, DIO24, DIO26, DIO27, DIO28, DIO30, DIO31, DIO32, DIO34, DIO35, DIO36.

Статические пользовательские площадки ввода/вывода: DIO1, DIO5, DIO9, DIO13, DIO17, DIO21, DIO25, DIO29, DIO33.