Основная информация

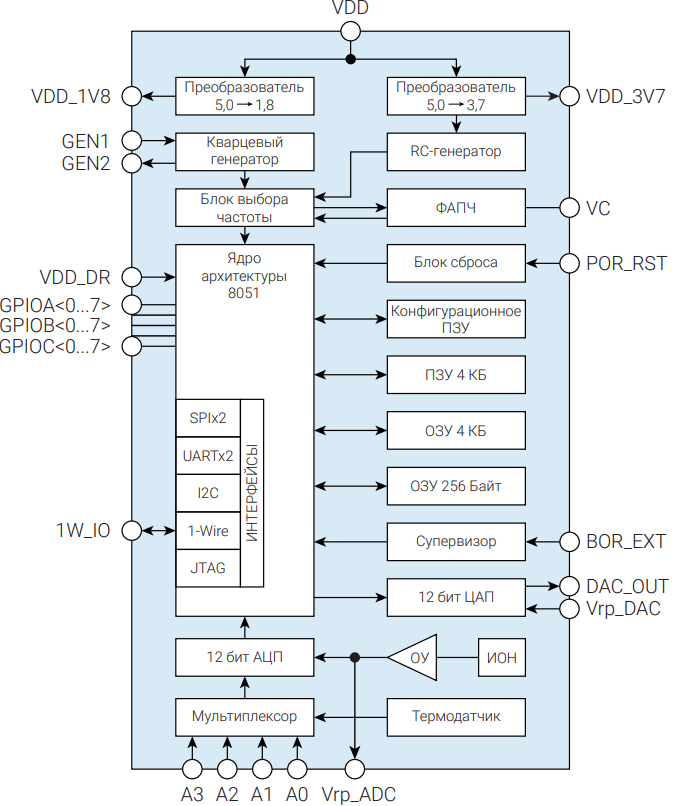

5400ТР105-003 – Сбоеустойчивый 8-ми разрядный контроллер с возможностью встроенного управления и конфигурирования аналого-цифровых блоков

Дата последнего обновления документации 25.08.2025

Особенности микроконтроллера

- Напряжение питания 5,0 В ± 5%

- Динамический ток потребления не более 10 мА (на частоте 8 МГц)

- Напряжение питания портов ввода/вывода GPIO: от 2,5 В до 5,0 В;

Вычислительное ядро:

- Система команд 8051

- Тактовая частота: до 8 МГц

- Машинный цикл: 1 такт

- Возможность выбора способа тактирования (кварцевый генератор, RC-генератор, внешний источник, ФАПЧ)

- Настраиваемые прерывания по внешним событиям

Память

Режим «HARD»:

- память программ 4 кБ (ОППЗУ);

- память данных 4352 байт внешней (большая и малая ОЗУ) и 256 внутренней ОЗУ (ядро 8051).

Режим «SOFT»:

- память программ 4 кБ (большая ОЗУ);

- память данных 256 байт внешней (малая ОЗУ) и 256 внутренней ОЗУ (ядро 8051).

Периферийные модули:

- 2 интерфейса SPI

- 2 интерфейса UART

- интерфейс I2C

- интерфейс 1-Wire

- интерфейс JTAG (программирование и отладка)

- 24 универсальные линии ввода/вывода GPIO с индивидуальной настройкой направления

- три 24-разрядных таймера/счетчика

- сторожевой таймер

- модуль перевода системы в режим пониженного энергопотребления (SLEEP)

- 4-х канальный 12-ти разрядный 200 кВыб/с АЦП

- 12-ти разрядный ЦАП

- ИОН + масштабирующий ОУ с возможностью настройки усиления

- RC-генератор с возможностью настройки частоты

- блок ФАПЧ с возможностью настройки коэффициента умножения

- супервизор питания

- термодатчик

- регуляторы напряжения электропитания

Электрические характеристики

| Параметр, единица измерения | Норма параметра | ||

|---|---|---|---|

| Не менее | Типовое | Не более | |

| Выходное напряжение линейных регуляторов (1), В | |||

| • 5,0B -> 3,7В (вывод VDD_3V7) | 3,5 | 3,7 | 4,2 |

| • 5,0B ->1,8В (вывод VDD_1V8) | 1,62 | 1,8 | 1,98 |

| Ток потребления микросхемы, мА | 8,0 | 18 | |

| Дифференциальная нелинейность ЦАП, МЗР | –0,99 | 3,0 | |

| Интегральная нелинейность ЦАП, МЗР | –8,0 | 8,0 | |

| Дифференциальная нелинейность АЦП(2), МЗР | –0,99 | 1,0 | |

| Интегральная нелинейность АЦП(2), МЗР | –4,0 | 4,0 | |

| Нижняя граница диапазона настройки частоты RC-генератора, кГц | 90 | ||

| Верхняя граница диапазона настройки частоты RC-генератора, кГц | 400 | ||

| Ток утечки портов ввода/вывода (GPIO), мкА | 0,01 | 20 | |

| Напряжение высокого уровня выходных цифровых сигналов, В | |||

| • при VDD_DR = 2,5B | VDD_DR-0,3 | 2,5 | |

| • при VDD_DR = 5,0B | VDD_DR-0,4 | 5,0 | |

| Напряжение низкого уровня выходных цифровых сигналов, В | |||

| • при VDD_DR = 2,5 B | 0 | 0,3 | |

| • при VDD_DR = 5,0 B | 0 | 0,4 | |

| Справочные данные (при T = 25°С) | |||

| Ток потребления микросхемы в режиме низкого энергопотребления («SLEEP»), мкА(3) | |||

| • при частоте тактирования ~ 300 кГц | 110 | ||

| • при частоте тактирования ~ 50 кГц | 80 | ||

- Линейные регуляторы предназначены для формирования внутреннего питания, нагрузка выводов VDD_3V7, VDD_1V8 недопустима.

- Расчет производится для преобразования с разрядностью равной 10 бит

- Задействованы блоки: ИОН, регуляторы напряжения, RC-генератор на низкой частоте, цифровая часть в режиме таймера

Электростатическая защита

Микросхема имеет встроенную защиту от электростатического разряда до 1000В по модели человеческого тела. Требует мер предосторожности.

Диапазон входных/выходных сигналов

| Параметр, единица измерения | Предельно-допустимый режим | Предельный режим | ||

|---|---|---|---|---|

| не менее | не более | не менее | не более | |

| Аналоговое напряжение питания (VDDA_5V), B | 4,5 | 5,25 | -0,1 | 5,35 |

| Цифровое напряжение питания (VDD_5V), B | 4,5 | 5,25 | -0,1 | 5,35 |

| Напряжение питания интерфейсной части (VDD_DR), В | 2,25 | 5,25 | -0,1 | 5,35 |

| Напряжение программирования ПЗУ (VPP_9V), В | 8,5 | 9,0 | -0,1 | 9,5 |

| Напряжение внешнего опорного уровня АЦП (Vrp_ADC), В | 2,25 | 5,0 | -0,1 | VDDA_5V |

| Напряжение внешнего опорного уровня ЦАП (Vrp_DAC), В | 2,25 | 5,0 | -0,1 | VDDA_5V |

| Напряжение высокого уровня входных цифровых сигналов (GPIO в режиме входа, BOR_EXT/PGM, TM, DBG, GEN1), В | VDD_DR–0,4 | VDD_DR+0,3(1) | -0,1 | VDD_DR+0,5(2) |

| Напряжение низкого уровня входных цифровых сигналов (GPIO в режиме входа, BOR_EXT/PGM, TM, DBG, GEN1), В | 0 | 0,4 | -0,1 | VDD_DR+0,52(2) |

| Нагрузочная способность GPIO, мА | ||||

| • при VDD_DR = 2,5 B | - | 1,5 | - | 3,0 |

| • при VDD_DR = 5,0 B | - | 3,0 | - | 5,0 |

| Нагрузочная способность вывода DAC_OUT(6), мА | - | 1,0 | - | 1,5 |

| Рабочая частота тактирования, МГц | - | 8,0 | - | 8,0 |

| Рабочая частота тактирования в режиме отладки(7), МГц | - | 8,0 | - | 8,0 |

| Температура эксплуатации, °С | -25(3) -45(4) -60(5) | +85 | -60 | +150 |

- не более 5,25 В

- не более 5,5 В

- для группы В

- для группы Б

- для группы А

- при включенном выходном буфере (бит DAC_BUF_EN = «1», регистр ANALOG_O_BUF)

- режим отладки – программирование и настройка микроконтроллера с использованием программы из встроенного ОЗУ в НКУ

Конфигурация и функциональное описание выводов

| № вывода | Тип вывода | Наименование вывода | Назначение вывода |

|---|---|---|---|

| 1 | DI/DO | GPIOB[5] | Порт ввода-вывода микроконтроллера, разряд №5 группы B |

| 2 | DI/DO | GPIOB[6] | Порт ввода-вывода микроконтроллера, разряд №6 группы B |

| 3 | DI/DO | GPIOB[7] | Порт ввода-вывода микроконтроллера, разряд №7 группы B |

| 4 | PWR | VDD_5V | Вывод цифрового положительного напряжения питания |

| 5 | AO | VC | Вывод блока ФАПЧ для подключения RC-фильтра |

| 6 | DI | GEN1 | Вход подключения кварцевого резонатора/вход для подачи внешней тактовой частоты |

| 7 | DO | GEN2 | Вход подключения кварцевого резонатора |

| 8 | PWR | VSSD | Вывод цифрового отрицательного напряжения питания |

| 9 | DI/DO | GPIOC[0]/TCK | Порт ввода-вывода микроконтроллера, разряд №0 группы C / вход TCK интерфейса JTAG в тестовом режиме (TM = 1) |

| 10 | DI/DO | GPIOC[1]/TMS | Порт ввода-вывода микроконтроллера, разряд №1 группы C / вход TMS интерфейса JTAG в тестовом режиме (TM = 1) |

| 11 | DI/DO | GPIOC[2]/TDI | Порт ввода-вывода микроконтроллера, разряд №2 группы C / вход TDI интерфейса JTAG в тестовом режиме (TM = 1) |

| 12 | DI/DO | GPIOC[3]/TDO | Порт ввода-вывода микроконтроллера, разряд №3 группы C / выход TDO интерфейса JTAG в тестовом режиме (TM = 1) |

| 13 | DI/DO | GPIOC[4] | Порт ввода-вывода микроконтроллера, разряд №4 группы C |

| 14 | DI/DO | GPIOC[5] | Порт ввода-вывода микроконтроллера, разряд №5 группы C |

| 15 | DI/DO | GPIOC[6] | Порт ввода-вывода микроконтроллера, разряд №6 группы C |

| 16 | DI/DO | GPIOC[7] | Порт ввода-вывода микроконтроллера, разряд №7 группы C |

| 17 | AO / PWR | VDD_1V8 | Вывод напряжения питания ядра (выходное напряжение LDO-регулятора 5,0В–1,8В) |

| 18 | PWR | VDD_DR | Вывод положительного напряжения питания универсальных портов ввода-вывода микроконтроллера 2,5 В – 5,0 В |

| 19 | DI/DO | 1W_IO | Вывод интерфейса 1-Wire (тип вывода – открытый сток) |

| 20 | DI/DO | GPIOA[0] | Порт ввода-вывода микроконтроллера, разряд №0 группы A |

| 21 | DI/DO | GPIOA[1] | Порт ввода-вывода микроконтроллера, разряд №1 группы A |

| 22 | DI/DO | GPIOA[2] | Порт ввода-вывода микроконтроллера, разряд №2 группы A |

| 23 | DI/DO | GPIOA[3] | Порт ввода-вывода микроконтроллера, разряд №3 группы A |

| 24 | DI/DO | GPIOA[4] | Порт ввода-вывода микроконтроллера, разряд №4 группы A |

| 25 | DI/DO | GPIOA[5] | Порт ввода-вывода микроконтроллера, разряд №5 группы A |

| 26 | DI/DO | GPIOA[6] | Порт ввода-вывода микроконтроллера, разряд №6 группы A |

| 27 | DI/DO | GPIOA[7] | Порт ввода-вывода микроконтроллера, разряд №7 группы A |

| 28 | DI | BOR_EXT/PGM | Вход внешнего супервизора питания/вход выбора режима программирования ПЗУ в тестовом режиме (TM = 1): лог. «1» – перевод в режим программирования, от шины отключается CPU и подключается JTAG; лог. «0» – стандартная работа. |

| 29 | DI | TM | Вход выбора режима работы микроконтроллера: лог. «1» – тестовый режим; лог. «0» – стандартная работа |

| 30 | DI | DBG | Вход для выбора блока памяти, выполняющего роль ПЗУ: лог. «1» – память ПЗУ (ROM_RAM_4KB) 4 КБ, ОЗУ 256 Б; лог. «0» – память ПЗУ (ROM_OTP_4KB) 4 КБ, ОЗУ 4 КБ + 256 Б. |

| 31 | DI | POR_RST | Вход для подключения внешнего конденсатора блока сброса |

| 32 | AI | Vrp_DAC | Вывод положительного опорного напряжения ЦАП |

| 33 | AO | DAC_OUT | Выход ЦАП |

| 34 | AI | VPP_9V | Вывод для программирования ПЗУ и конфигурационной памяти |

| 35 | PWR | VDDA_5V | Вывод аналогового положительного напряжения питания |

| 36 | AO / PWR | VDD_3V7 | Вывод питания RC-генератора (выходное напряжение LDO-регулятора 5,0 В–3,7 В) |

| 37 | PWR | VSSA | Вывод аналогового отрицательного напряжения питания |

| 38 | AI/AO | Vrp_ADC | Вывод положительного опорного напряжения АЦП/выход масштабирующего ОУ (если ОУ включен в ходе настройки конфигурационной памяти) |

| 39 | AI | A0 | Вход 0-го канала АЦП |

| 40 | AI | A1 | Вход 1-го канала АЦП |

| 41 | AI | A2 | Вход 2-го канала АЦП |

| 42 | AI | A3 | Вход 3-го канала АЦП |

| 43 | PWR | VDD_tech | Технологический вывод (объединить с VDD_5V и/или VDDA_5V) |

| 44 | DI/DO | GPIOB[0]/H_S | Порт ввода-вывода микроконтроллера, разряд №0 группы B/выбор режима конфигурационной памяти в тестовом режиме(TM = 1):лог. «1» – источником данных конфигурационной памяти являются регистры; лог. «0» – источником данных конфигурационной памяти является ПЗУ. |

| 45 | DI/DO | GPIOB[1]/RC_CLKOUT | Порт ввода-вывода группы B / частота RC-генератора в тестовом режиме (TM = 1) |

| 46 | DI/DO | GPIOB[2] | Порт ввода-вывода микроконтроллера, разряд №2 группы B |

| 47 | DI/DO | GPIOB[3] | Порт ввода-вывода микроконтроллера, разряд №3 группы B |

| 48 | DI/DO | GPIOB[4] | Порт ввода-вывода микроконтроллера, разряд №4 группы B |

DI - цифровой вход; DO - цифровой выход; AI - аналоговый вход; AO - аналоговый выход; PWR - вывод напряжения питания

Эквивалентные схемы

Рекомендуемая схема применения

Конденсаторы высокочастотные керамические, либо сдвоенные. В случае сдвоенных конденсаторов, один из них обязательно должен быть высокочастотный керамический емкостью не менее 10 нФ. Шунтирующие конденсаторы должны располагаться на плате в непосредственной близости к соответствующим выводам микросхемы.

| Компонент | Номинал | Компонент | Номинал |

|---|---|---|---|

| R1 | 1 – 2 МОм | C3 | 10 нФ |

| R2 | 2 – 20 кОм | C4 | 1 нФ |

| R3 | 100 Ом | C5 | 20 нФ |

| R4 | 4,7 кОм | С6 – C13 | 100 – 200 нФ |

| C1, С2 | 16 – 64 пФ | ZQ | кварцевый резонатор с частотой до 8 МГц |

Важные замечания при работе с микросхемой

- Если 1-Wire интерфейс не используется, то вывод 1W_IO(19) необходимо оставить в обрыве.

- При использовании I2C интерфейса необходимо выводы SDA и SCL подтянуть резисторами 4,7 кОм к питанию.

- Если ФАПЧ не используется, то вывод VC(5) подключить к VSSA(37).

- При использовании внешнего генератора, вывод GEN2(7) необходимо оставить в обрыве.

- При использовании внутреннего RC-генератора вывод GEN1(6) необходимо объединить с VSSA, вывод GEN2(7) оставить в обрыве.

- Если размах цифровых уровней генератора 5,0 В, а напряжение питания портов ввода-вывода отлично от 5,0 В (например, 3,3 В или 2,5 В), то в конфигурационной памяти необходимо выбрать источник тактирования «Кварцевый резонатор» (GEN1_QV или GEN1_QV+PLL) путем записи советующих бит в регистр ANALOG_O_PLL.

- При использовании внутреннего супервизора питания (бит BOR = «0», регистр ANALOG_O_RC_R), вывод BOR_EXT/PGM необходимо подключить к VSSD.

- Если ЦАП не используется, то вывод Vrp_DAC(32) необходимо подключить к VSSA(37).

- Если АЦП не используется, то выводы A3–A0 необходимо подключить к VSSA(37).

- На выводы Vrp_DAC и Vrp_ADC задается внешнее опорное напряжение для блоков АЦП и ЦАП. Есть возможность формирования внутреннего опорного напряжения с помощью масштабирующего операционного усилителя (МОУ). Для этого необходимо включить МОУ (бит OA_EN = «1», регистр ANALOG_O_BUF) и настроить коэффициент масштабирования (биты OA_GAIN_N, OA_GAIN_M, регистр ANALOG_O_BUF). Данное напряжение можно проконтролировать на выводе Vrp_ADC. Это же напряжение можно подать и на вход опорного уровня ЦАП с помощью внешнего соединения выводов Vrp_ADC и Vrp_DAC.

При TM=«1» микросхема работает в тестовом режиме (подробнее см.Конфигурационная память (ANALOG_CFG)), H_S=«1» (источником

данных конфигурационной памяти являются регистры) и бит регистра ANALOG_O_RC_R REF_OUT_DISABLE=«0», то выход 39 работает как тестовый вывод опорного напряжения.

В данном режиме нельзя! подключать вывод 39 к VSSA(37), т.к. данный опорный уровень вместе с линейными регуляторами

формирует питание аналоговой и цифровой частей микросхемы.

-

В случае перехода в тестовый режим и когда источником данных конфигурационной памяти являются регистры (H_S=«1») рекомендуется всегда записывать в бит REF_OUT_DISABLE регистра ANALOG_O_RC_R лог. «1».

-

В случае перехода в тестовый режим и когда источником данных конфигурационной памяти является ПЗУ (H_S = «0») в бите REF_OUT_DISABLE регистра ANALOG_O_RC_R по умолчанию уже записана лог. «1».

Также биты V_REF в регистре ANALOG_O_REF являются технологическими и уже настроены и прошиты в ПЗУ на этапе производства. При прожиге конфигурационной памяти следует убедиться, что данные биты не содержат лог «1».