Тактирование

Выбор источника тактирования

Источник тактирования определяется схемотехнически одним из двух вариантов:

-

С помощью встроенного генератора на внешнем кварцевом резонаторе, подключенного к выводам TP_QI (28) и TP_QO (27). Выход генератора должен TP_FQO (26) быть подключен на тактовый вход CLK60 (39). Для работы генераторы требуется подать на вывод VDDIO2 питание, равное питанию VDDIO. Генератор может работать с кварцевыми резонаторами с номиналом по частоте от 2 МГц до 20 МГц. Следует учитывать, что выход на режим генератора составляет от нескольких миллисекунд.

-

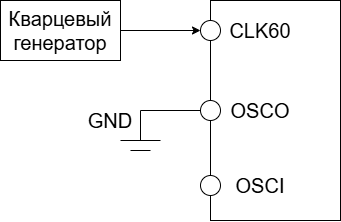

С помощью внешнего тактового генератора с частотой в диапазоне 10 МГц...60 МГц, подключенного к выводу CLK60 (39). Вывод TP_QI (28) должен быть подключен к VDDD3P3 (25), вывод TP_QO (27) должен быть подключен к GND.

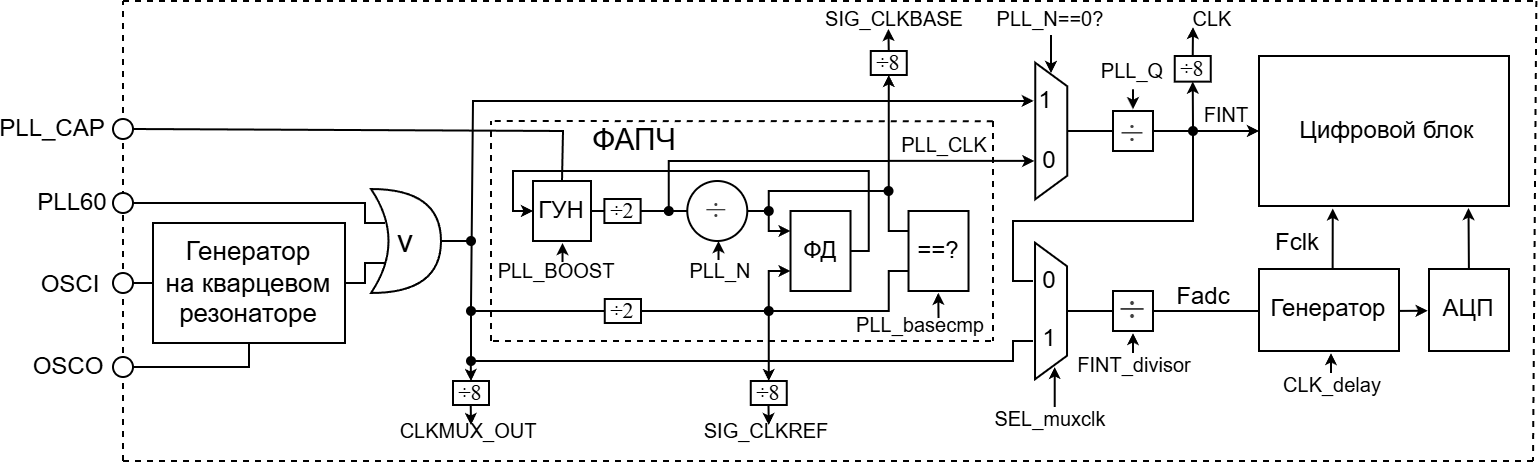

Настройка умножителя частоты в ФАПЧ

Умножитель частот может быть задействован, если входная частота тактирования не более 20 МГц. Для включения умножителя требуется задать PLL_N в диапазоне 3...74. Если поле PLL_N равно нулю, то цифровой блок использует тактирование со входа микросхемы.

Частота сигнала CLK_PLL с выхода умножителя определяется произведением входной частоты на коэффициент (PLL_N) и не должна превышать 60 МГц.

Время установления частоты и величина пульсаций определяется номиналом петлевого фильтра, состоящего из внутреннего резистора 10 кОм и внешнего конденсатора, подключенного к выводу PLL_CAP. При увеличении емкости (относительно номинала 0,1 мкФ) уровень пульсаций уменьшается, однако время выхода на режим увеличивается. При уменьшении номинала время установления частоты уменьшается, однако уровень пульсаций увеличивается. Уровень пульсаций не должен превышать 5% от частоты.

Для ускорения зарядки петлевого фильтра (уменьшения времени переходного процесса) требуется задать бит PLL_boost в единицу. Момент отключения предзаряда петлевого фильтра определяется полем PLL_basecmp регистра PLL_config. При его задании включается счетчик импульсов опорной частоты CLKREF и частоты с выхода делителя PLL_BASE. Компаратор удерживает сигнал сброса до того момента пока количество импульсов с делителя ГУН не будет превышать количество испольсова опорной частоты CLK_REF на 2^PLL_basecmp импульсов. Сигнал готовности компаратора выведен на бит SPI CLKCOMP_rdy.

Для анализа работы ФАПЧ в микросхеме предусмотрен отладочный вывод DB. При записи в поле DB_mode регистра AFE_config одного из значений "0", "1", "2", "3" на выводе DB будет выведены один из сигналов CLKMUX_OUT, DB_SIG_PLLBASE, DB_SIG_CLKREF,CLK поделенные на 8.

Настройка частоты FINT

Для деления входной частоты требуется задать поле PLL_Q регистра PLL_config значением в диапазоне 1..15. Если делить частоту не требуется, то задать PLL_Q нулем.

Для компенсации длительного выхода на рабочий режим источника тактирования (внешний тактовый генератор или внутренний генератор на кварцевом резонаторе) требуется ввести значение в диапазоне 1..3 поля CLK_delay регистра PLL_config. В этом случае тактируемая цифровая логика будет удерживаться в состоянии «сброс».

Настройка частоты АЦП

С помощью бита SEL_muxclk определяется источник тактирования АЦП. При использовании встроенного ФАПЧ для тактирования АЦП рекомендуется использовать сигнал напрямую с кварцевого генератора. Для работы АЦП требуется обеспечить тактирование с частотой Fadc не превышающей 20 МГц, для чего пользователь должен выбрать делитель частоты FINT_divisor. Для одного преобразования АЦП требуется 16 тактов Fadc, а для работы следящего контура требуется не менее 32 тактов FINT. Если время цикла работы следящего контура превышает время одного преобразования АЦП, то пользователю необходимо замедлить АЦП добавлением пустых тактов Fadc. Их количество определяется битами DELAY_cycles .

Выключение тактирования

Для снижения энергопотребления, когда микросхема запитана, но не используется, имеется возможность выключить тактирование с цифрового блока с помощью бита OSC_DIS или подачей активного уровня 1 на вывода STNDBY. Состояние включено/выключено тактирование может быть определено по биту CLK_rdy.