Интерфейс SPI

Описание структуры SPI

Взаимодействие управляющего микроконтроллера с микросхемой 5400ТР065А-022 осуществляется через последовательный SPI интерфейс с помощью четырех сигналов: SCLK, SSTR, SDO, SDI.

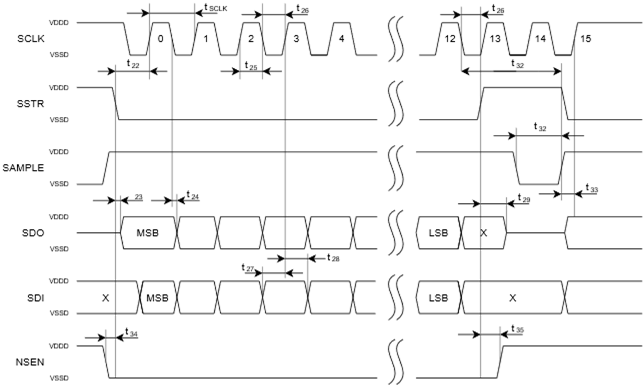

- SSTR — сигнал разрешения работы контроллера. Активный уровень "0". Переход из 1 в 0 является событием начала транзакции (или цепочки транзакций). При SSTR = 1 производится сброс счетчиков синхроимпульсов SCLK.

- SCLK — сигнал синхронизации. Микросхема защелкивает входные данные (вход SDI) по переднему фронту SCLK и выставляет выходные данные SDO по заднему фронту SCLK. Ведущее устройство должно принимать данные с входа SDO по переднему фронту и передавать SDI по заднему фронту SCLK.

- SDI — порт для приема и выдачи данных. Выдача данных на порт производится только при однократном переводе контроллера SPI в режиме полудуплексного чтения.

- SDO — порт выдачи данных, при неактивном уровне SSTR, SDO всегда переводится в состояние высого импеданса ("Z")

Контроллер SPI работает только по синхроимпульсам SCLK и не зависит от наличия системной частоты FINT. Взаимодействие с контроллером осуществляется через последовательности кадров. Каждый кадр состоит из 16 полных синхроимпульсов SCLK (имеющих и передний, и задний фронт).

- Контроллер имеет два 4-битных счетчика:

- Счетчик синхроимпульсов запроса (инкрементируется передними фронтами SCLK)

- Счетчик синхроимпульсов ответа (инкрементируется задними фронтами SCLK)

- При SSTR = 1 счетчики сброшены.

- При наступлении 17-го синхроимпульса счетчики переполняются, что сигнализирует о начале нового кадра (позволяет использовать DMA).

Существуют три вида кадра

- прием на SDI командного слова и одновременная выдача на SDO данного по предыдущему адресу

- прием на SDI данного для записи (на выводе SDO выдается существующее данное по адресу записи)

- выдачей данного на SDI в полудуплексном режиме (вывод SDO дублирует выдачу SDI)

Формат командного слова: М₂,М₁,М₀, A10,A9,A8, A7, A6, A5, A4, A3, A2, A1, A0, 0, P

- M₂, M₁, M₀ — код операции (см. таблицу ниже)

- A₁₀...A₀ — адрес

- P — бит четности

Коды операций

| Код операции (М₂,М₁,М₀) | Описание |

|---|---|

| 100 | Запись по адресу значением из следующего кадра |

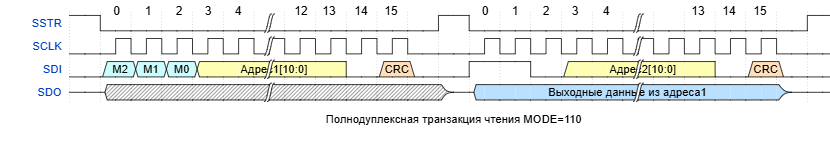

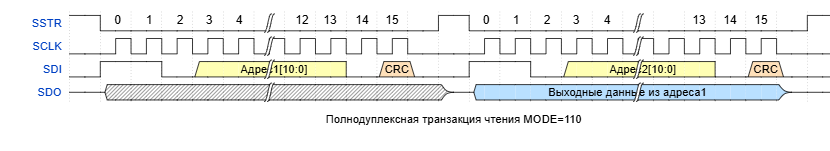

| 110 | Вывод значения ячейки по адресу в следующем кадре (полнодуплексная транзакция) |

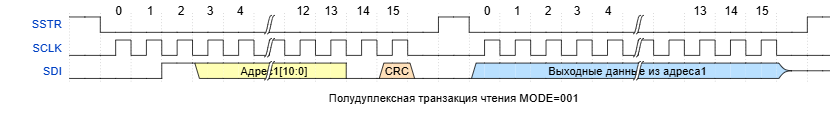

| 001 | Вывод значения ячейки по адресу в следующем кадре (полудуплексная транзакция) |

| 010 | Команда блокировки значения в выходном регистре |

| 101 | Команда разброкировки записи выходного регистра |

Контроллер SPI может находится в одном из 3 состояний:

- Прием командного слова

- Прием слова данных (если предущее командное слово интерпретировалось как запись)

- Выдача слова данных в полудуплексном режиме

Коды операции "110", "010", "101" оставляют контроллер SPI в 1 состоянии, следущий кадр может содержать командное слова, а на выводе SDO будет передаваться значение адреса зафиксированного в предыдущем кадре.

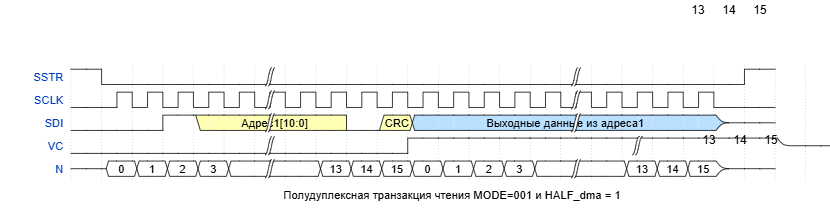

Переход в 2,3 состояние из состояния 1 возможен при корректно принятым командным словом с кодом операции "110" "001". При нахождении контроллера в 2 и 3 сотояниии данные на выводе SDI не интепретируются как командное слово, по окончании кадра контроллер переходит в состояние 1.

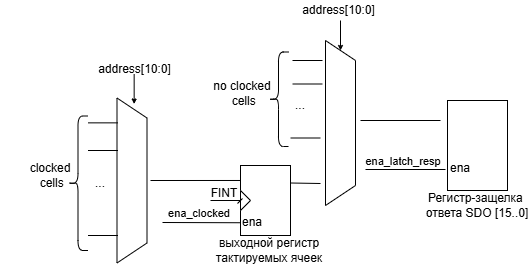

Доступ к ячейкам памяти — параллельный: один мультиплексор подключает нужную ячейку к контроллеру SPI по заданному адресу.

Фиксация адреса, мультиплексирование по адресу регистра для чтения производится при приеме 14-го переднего фронта командного слова, не дожидаясь завершения окончания транзакции и приема бита четности. Однако контроллер перейдет в другое состояние только если поступило 16 передних фронтов SCLK, 14-й бит регистра запроса равен 0 и корректен бит четности (или отключен контроль).

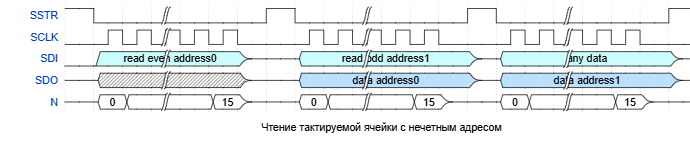

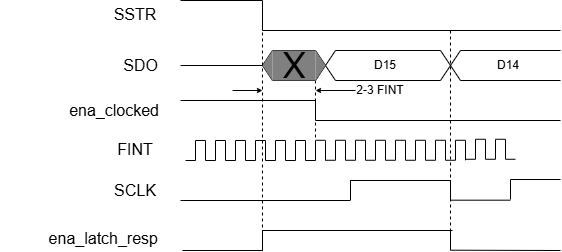

Для тактируемых FINT ячеек выход мультиплексора подключен к промежуточному регистру. Разрешение копирования данных на него снимается "ena_clocked' при заднем фронте SSTR или 16-м заднем фронте SCLK (при непрерывной циклической передаче). Сигнал "ena_clocked' (см. рис.##) пересинхронизируется двумя триггерами на FINT, что требует паузы до первого фронта SCLK длиной в 3 периода FINT (параметр данной задержки конфигурируется в большинстве архитектур микроконтроллеров). Нечетные адреса всех тактируемых ячеек защелкиваются в промежуточный регистр только при чтении четного адреса на единицу меньше. При повторном чтении нечетного адреса значение в промежуточном регистре не обновится. Для чтение актуального значения нечетного адреса возможно при последовательной передаче транзакций команд чтения сначала четного адреса, затем нечетного адреса на единицу больше.

Выходной регистр-защелка не может поменять свое значение начиная с 1 по 15 заднего фронта SCLK.

Контроллер SPI может быть переведен в режим полудуплексной передачи без перевода SSTR в 1 (циклический режим). В этом случае требуется установить бит HALF_dma = 1, что даст указание контроллеру переводить вывод SDI и приемо-передатчик сигналом VC в активное состояние выдачи на спаде 16 SCLK текущего кадра приема командного слова.

Вывод nSEN маскирует сигнал SSTR. При nSEN = 1 интерфейс SPI отключается (используется при подключении нескольких микросхем). Если обмен только с одной микросхемой, nSEN должен быть подтянут к 0.

Временные параметры последовательного интерфейса

| Параметр, единица измерения | не менее | типовое??? | не более |

|---|---|---|---|

| Период SCLK (t_SCLK), нс | 50 | ||

| Задержка от заднего фронта SSTR до переднего фронта SCLK (t_22), нс | 6,0 | ||

| Задержка от заднего фронта SSTR до занятия линии SDO (t_23), нс | 39 | ||

| Задержка от заднего фронта SCLK до переключения SDO (t_24), нс | 41 | ||

| Длительность лог. «1» на SCLK (t_25), нс | 16 | ||

| Длительность лог. «0» на SCLK (t_26), нс | 16 | ||

| Задержка от выставления SDI до переднего фронта SCLK (t_27), нс | 6,0 | ||

| Задержка от переднего фронта SCLK до изменения SDI (t_28), нс | 6,0 | ||

| Задержка от заднего фронта SSTR до освобождения SDO (t_29), нс | 29 | ||

| Задержка от заднего фронта SCLK до переднего фронта SSTR (t_30), нс | 6,0 | ||

| Задержка от заднего фронта SCLK при SSTR=0 до переднего фронта Sample (t_31), нс | 6,0 | ||

| Длительность лог. «0» на Sample (t_32), нс | 50 | ||

| Задержка от переднего фронта Sample до первого переднего фронта SCLK при SSTR=0 (t_33), нс | 4,0 | ||

| Задержка от заднего фронта nSEN до заднего фронта SSTR (t_34), нс | 0 | ||

| Задержка от переднего фронта SSTR до переднего фронта nSEN (t_35), нс | 0 |

Дополнительные режимы SPI

Целевое применение 5400ТР065А-022 - идуктивные датчики угла и положения в аппаратуре специального назчения. Для снижения уровня помех и искажений рекомендуется размещение 5400TP065A-022 в непосредственной близости от источника ЭДС. Для обеспечения цифроврого обмена рекомедуется использование дифференциальных пар - передача сигналов по току (RS-485, M-LVDS, LVDS и др.). Для повышения надежности передачи данных и упрощения использования множества преобразвоателей в микросхеме 5400ТР065А-022 реализовано несколько допольнительных фукнций.

Фиксация значения выходной ячейки для множественного чтения.

При передаче кода операции "010" сигнал разрешения с регистра (четный и нечетный адрес) тактируемых ячеек маскируется, значение его не обновляется. Это дает возможность прочитать значения несколько раз и сравнить целостность передачи данных. Разблокировка производится кодом операции "101".

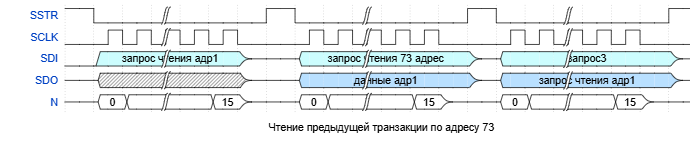

Чтение ранее переданной транзакции

Чтение адреса 73 SPI_req возвращает ранее переденный в контроллер SPI кадр. Это позволяет проверить соответствие принятого значения с запрошенным адресом.

Блокировка записи слов

При записи в регистр WR_Lock значения отличного от нуля, запись в другие регистры блокируется (кроме BUS_addr), только чтение.

Программный адрес

При наличии нескольких микросхем подключенных к одной общей шине для обеспечения индивидуального доступа к каждой микросхеме в их регистры IC_addr могут быть предварительно записаны различные номера в диапазоне [1..255]. Чтобы команда чтения или записи сработала для конкретной микросхемы мастер устройство должно предваритально записать в регистр BUS_addr значение номера необходимой микросхемы, и затем затем следущие необходимые транзакции записи и чтения. Запись в регистр BUS_addr не блокируется значенями регистров WR_Lock и IC_addr.

Контроллер SPI кокретной микросхемы реагирует на команды только в следующих случаях

- значение IC_addr равно 0

- IC_addr != 0, BUS_addr == IC_addr

- IC_addr != 0, BUS_addr == 0, флаг BUS0_mode == 1

В остальных случаях котроллер не реагирует (за исключением перезаписи BUS_addr).

Подразумевается, что конкретное значение IC_addr записывается в ПЗУ микросхемы до установки в общий интерфейс аппаратуры.

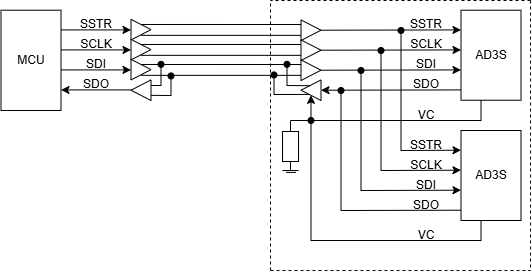

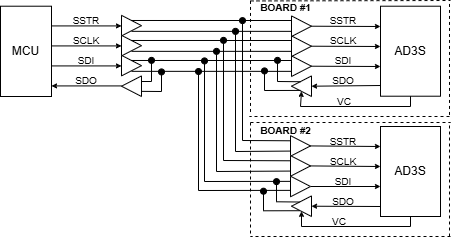

Управление внешним приемо-передатчиком с помощью вывода VC

Установка бита VC_mode в 1 регистра AFE_config переводит вывод VC в режим управления внешним приемо-передатчиком. Бит DE_half опеределяет когда вывод VC переходит в активное состояние: при DE_half = 1 - только для ответа при полудуплексных запросах, при DE_half = 0 при всех запросах когда микросхема должна отвечать (когда SSTR = 0, nSEN = 0 и есть соответствие адреса микросхемы и шины адреса). Бит DE_inv определяет какой уровень VC является активным для передатчика: при DE_inv = 0 активный 1, при DE_inv = 1 активный уровень 0. Установка бита DE_turnZ в 1 переводит вывод VC в состояние высокого импеданса ( "Z" ) между передачами, а сигнал VC должен быть доопределен подтяжкой резистора (требуется при подключении нескольких микросхем к одному передатчику). На рисунках ниже представлены некоторые варианты включения микросхемы.

Режим параллельной передачи результата

Режим включается при SPI_ext_en = 1. Выводы ENC1_A, ENC1_B, ENC1_0, ENC2_A, ENC2_B, ENC2_0 переключаются параллельно с SDO и передают данные из регистров C1Coord/C2Coord, C1CoordHB/C2CoordHB, C1Vel/C2Vel, C1VelHB/C2VelHB.

Назначение выводов в режиме параллельной передачи результата

| SDI | VC | ENC1_A | ENC1_B | ENC1_0 | SDO | ENC2_A | ENC2_B | ENC2_0 |

|---|---|---|---|---|---|---|---|---|

| 0 | 0 | C1Coord | C1Vel | C1CoordHB | C1VelHB | C2Coord | C2Vel | C2CoordHB |

| 0 | 1 | C1Vel | C1Coord | C1VelHB | C1CoordHB | C2Vel | C2Coord | C2VelHB |

| 1 | 0 | C2Coord | C2Vel | C2CoordHB | C2VelHB | C1Coord | C1Vel | C1CoordHB |

| 1 | 1 | C2Vel | C2Coord | C2VelHB | C2CoordHB | C1Vel | C1Coord | C1VelHB |