Постоянное запоминающее устройство

Структура

Микросхема содержит два сегмента ПЗУ для хранения пользовательских настроек, необходимых для автоматической инициализации регистров микросхемы после подачи питания или подачи сигнала "сброс".

ПЗУ с параллельным доступом

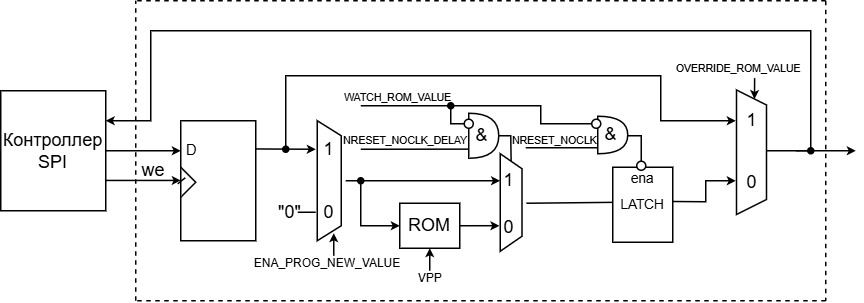

ПЗУ с параллельным доступом включается непосредственно при установлении питания, содержит 2 ячейки ПЗУ, неразрывно связанных управляющими регистрами PLL_config и INIT_conf. На рисунке предсталена структура ячейки ПЗУ.

Доступ к настройкам PLL_config и INIT_conf осуществляется через управляющий регистр UOTP_ctrl, содержащий три бита WATCH_ROM_UVAL, PROG_NEW_UVAL, OVERRIDE_UVAL. По умолчанию значения PLL_config и INIT_conf равны нулю. Для временного переопределения этих значений (до снятия питания) необходимо записать в соответствующие регистры (PLL_config и INIT_conf) требуемые данные и записать в бит OVERRIDE_UVAL лог. «1». При этом записанные значения сохраняются даже при подаче программного сброса через бит MANUAL_NRST_PLL (запись нуля, затем единицы). Для программирования данных значений в ПЗУ требуется предварительно записать в регистры PLL_config и INIT_conf нужные параметры, убедиться в корректности записи прочитав их (OVERRIDE_UVAL =1), далее установить бит PROG_NEW_UVAL и подать напряжение программирования VPP. Через определенное время необходимо снять напряжение VPP, сбросить бит PROG_NEW_UVAL, записать в бит WATCH_ROM_UVAL лог. «1», считать значения PLL_config, INIT_conf и убедиться в их корректности. В случае отсутствия необходимых запрограммированных значений, повторить операцию.

ПЗУ с последовательным доступом

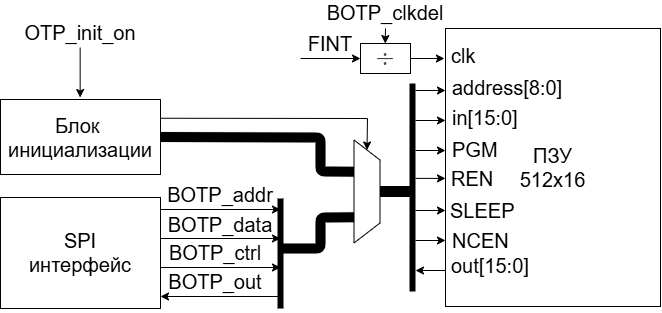

Второй сегмент ПЗУ предназначен для инициализации регистров конфигурации и ячеек памяти микровычислителей при включении питания. ПЗУ содержит 512 16-битных слов. Если выставлен бит OTP_init_on, после снятия сигнала сброс (при наличии тактирования), контроллер инициализации последовательно считывает данные ячеек ПЗУ и записывает в соответствующие регистры. Порядок записи жестко определен и неизменен.(см таблицу 8).

Таблица 8. Соответствие адресов ячеек памяти ПЗУ и конфигурационных регистров

| + | 2 x 0 | 2 x 1 | 2 x 2 | 2 x 3 | 2 x 4 | 2 x 5 | 2 x 6 | 2 x 7 |

|---|---|---|---|---|---|---|---|---|

| 2 x 0 | 0 cpu1 | 1 cpu1 | 2 cpu1 | 3 cpu1 | 4 cpu1 | 5 cpu1 | 6 cpu1 | 7 cpu1 |

| 2 x 8 | 8 cpu1 | 9 cpu1 | 10 cpu1 | 11 cpu1 | 12 cpu1 | 13 cpu1 | 14 cpu1 | 15 cpu1 |

| 2 x 16 | 16 cpu1 | 17 cpu1 | 18 cpu1 | 19 cpu1 | 20 cpu1 | 21 cpu1 | 22 cpu1 | 23 cpu1 |

| 2 x 24 | 24 cpu1 | 25 cpu1 | 26 cpu1 | 27 cpu1 | 28 cpu1 | 29 cpu1 | 30 cpu1 | 31 cpu1 |

| ... | ... | ... | ... | ... | ... | ... | ... | ... |

| 2 x 232 | C1KampS | C1KampC | C1KbiasS | C1KbiasC | C1fbias | C1ExPhShft | C1ExoStngs | C1EXInc |

| 2 x 240 | C1Amp_th | C1InputStngs | C1Lock_th | C1Zero | C1Mask | C1KonturStngs | C1ResGntr1 | C1Vcnt_bound |

| 2 x 248 | 233 cpu1 | 234 cpu1 | 235 cpu1 | 236 cpu1 | 233 cpu2 | 234 cpu2 | 235 cpu2 | 236 cpu2 |

| 2 x 256 | 0 cpu2 | 1 cpu2 | 2 cpu2 | 3 cpu2 | 4 cpu2 | 5 cpu2 | 6 cpu2 | 7 cpu2 |

| ... | ... | ... | ... | ... | ... | ... | ... | ... |

| 2 x 484 | 232 cpu2 | C2KampS | C2KampC | C2KbiasS | C2KbiasC | C2fbias | C2ExPhShft | C2ExoStngs |

| 2 x 492 | C2EXInc | C2Amp_th | C2InputStngs | C2Lock_th | C2Zero | C2Mask | C2KonturStngs | C2ResGntr1 |

| 2 x 500 | C2Vcnt_bound | IC_addr | ADC_config | Mask_Stat | Flags_delay | MR_lock | CMP_lth | AFE_config |

| 2 x 508 | Mode_config | – | – | – | – | – | – | – |

Запись и чтение ПЗУ производится с помощью управляющих регистров BOTP_addr, BOTP_data, BOTP_out, BOTP_ctrl.

Для корректной работы ПЗУ требуется настройка тактирования. Исходя из значения частоты FINT требуется записать в регистр BOTP_clkdel такое значение для деления частоты FINT (в соответствии с таблицей из описания регистров), чтобы тактовая частота на блок ПЗУ не превышала 10 МГц.

Для записи данных в ячейку ПЗУ по указанному адресу требуется записать целевой адрес в регистр BOTP_addr, а записываемое значение — в регистр BOTP_data. Установить бит NCEN в лог. «0», бит SLEEP в лог. «0», бит PGM в лог. «1». Затем подать напряжение VPP. Через определенное время снять напряжение VPP, сбросить бит PGM, установить бит REN и проверить записанное значение с помощью считывания ячейки BOTP_data.