Программируемый генератор

Программируемый генератор

Микросхема содержит два независимых программируемых генератора, формирующих опорный сигнал на выводах EXO1/EXO2. Питание выходного буфера генератора подводится непосредственно с выводов VDD_EXO1/VDD_EXO2, GND_EXO1/GND_EXO2. Напряжение питания генератора не зависит от напряжения VDDD, VDDA и выбирается исходя из конкретной схемы усилителя возбуждения в диапазоне от 3,3 В до 5,0 В.

С помощью настройки EXO_mode выбирается режим работы генератора:

EXO_mode = 00— генератор выключенEXO_mode = 01— вывод синусоидального сигналаEXO_mode = 10— вывод импульсного сигналаEXO_mode = 11— вывод постоянного уровня

Для включения одного из режимов необходимо выбрать соответствующий режим и выставить биты EXO1_en/EXO2_en регистра Mode_config в единицу.

Генератор синусоидальных сигналов

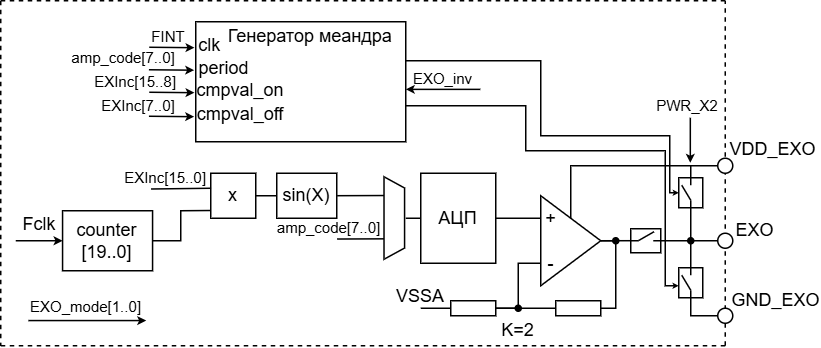

На рисунке ниже представлена структурная схема генератора сигналов.

В цифровом формирователе кода на каждом такте Fclk инкрементируется 20-ти разрядный счетчик, значение которого перемножается на 16-битный коэффициент C1EXInc, C2EXInc. Далее для [19:12] разрядов произведения ставится в соответствие знаковое 8-ми разрядное значение единичного синуса, затем перемножается на беззнаковый коэффициент (176 + AMP_CODE) / 1024 и для обеспечения линейности усиления на выходном буфере добавляется значение 63 - AMP_CODE / 4. Полученное 8-ми разрядное значение переводится в напряжение с опорным сигналом 2,5 В и усиливается выходным буфером с коэффициентом 2 относительно 0 В.

По формуле (1) определяется частота сигналов fex, по формуле (2) задается амплитуда сигналов Vexo:

Частоты fex1, fex2 выбираются исходя из спецификации датчика. Пользователь осуществляет восстановление (фильтрацию) и усиление сигналов генераторов перед подачей на датчики.

Для исключения нелинейности усиления коэффициент AMP_Code должен быть выбран таким образом, чтобы значение Vamp было ниже напряжения питания выходного буфера VDD_EXO1/VDD_EXO2 как минимум на 0,4 В.

Опорное напряжение для ЦАП может быть в диапазоне [2.5В ... 3.3В], и должно быть подано на вывод REFDAC. Имеется возможность использовать внутренний ИОН, для чего требуется установить бит VREF_DAC_en в единицу. И в том и другом случае требуется шунтирование вывода REFDAC кондесатором 0.1мкФ.

Генерация импульсного сигнала

Генерация импульсного сигнала выполняется 8-битным счетчиком тактируемым системной частотой FINT. Частота импульсов определяется значением Amp_code[7:0] в соответствии с формулой (3):

Скважность меандра определяется 8-битными значениями EXInc[15:8], EXInc[7:0] регистров C1EXInc/C2EXInc. Когда значение 8-битного счетчика равно EXInc[15:8], на выводе EXO1/EXO2 устанавливается уровень VDDEXO1/VDDEXO2, когда значение счетчика равно EXInc[7:0], выход подключается к GNDEXO1/GNDEXO2. Если задать бит EXO_inv регистра C1ExoStngs/C2ExoStngs, то выход инвертируется. При выставлении бита PWR_X2 регистра C1ExoStngs/C2ExoStngs ток коммутации вывода EXO1/EXO2 на VDDEXO1/VDDEXO2 и GNDEXO1/GNDEXO2 будет увеличен в 2 раза. Для синхронизации двух 8-битных счетчиков в импульсном режиме требуется установить бит EXO_sync в регистре AFE_config в единицу.

Вывод постоянного импульса

В режиме постоянного уровня, на выходе EXO1/EXO2 будет формироваться напряжение в соответствии с формулой (4):

Пользователь должен убедиться, что напряжение питания VDDEXO1/VDDEXO2 превышает расчетное значение Vexo.